# Helion Technology

## OVERVIEW DATASHEET - High Performance AES (Rijndael) cores for ASIC

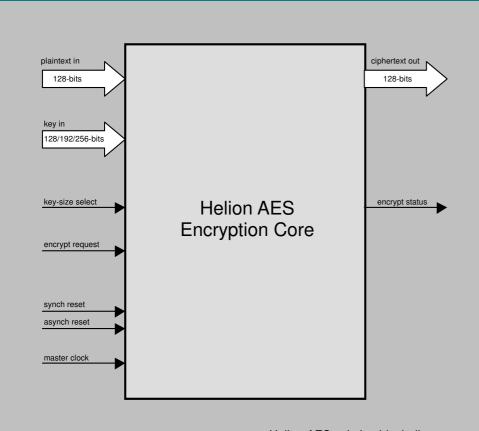

Helion AES solution block diagram

#### **Features**

- Implements AES (Rijndael) to latest NIST FIPS PUB 197

- Full dynamic support for all AES key sizes (128, 192 and 256-bits)

- Four versions available; user can choose best balance of speed and size for application

- Fastest version supports data rates well in excess of 40Gbps

- Separate cores provided for encryption and decryption

- Roundkey generation can be split out for ultra low gatecount implementations

- All AES operating modes easily implemented (eg. ECB, CBC, OFB, CFB, CTR, CCM, GCM, XTS, OCB)

- Simple external interface

- Suitable for use in ASIC or fine-grain FPGA technologies

#### **Deliverables**

- Fully synthesisable RTL VHDL or Verilog source code

- VHDL or Verilog testbench with FIPS test vectors

- Synopsys synthesis scripts

- User documentation

## Overview

These high performance cores from Helion are intended for use in ASIC and fine-grain FPGA technologies, and implement the AES (Rijndael) encryption standard, as described in the NIST Federal Information Processing Standard (FIPS) Publication 197 document.

Designed with ultimate flexibility in mind, the cores offer both encryption and decryption functions, plus they support any or all of the available key-sizes (128/192/256-bit). Helion was the very first company in the world to offer commercial AES solutions in hardware back in 2001, and given this head start, our cores are now extremely well proven in numerous real products. These cores are extremely simple to use, and highly versatile; they can be integrated into any AES design requirement with minimum effort.

## **Helion Technology Limited**

Ash House, Breckenwood Rd, Fulbourn, Cambridge CB21 5DQ, England.

# The Helion AES core range

## **Functional Description**

The Helion AES cores implement the 128-bit block-size NIST FIPS AES algorithm. The encryptor core accepts a 128-bit plaintext input word, and generates a corresponding 128-bit ciphertext output word using a supplied 128, 192, or 256-bit AES key. The decryptor core provides the reverse function, generating plaintext from supplied ciphertext, using the same AES key as was used for encryption.

The encryption and decryption cores are supplied as standard with hardware roundkey expansion logic included, so that they form a complete stand-alone AES solution, as described above. However, Helion has designed the roundkey expansion logic as a discrete building block; and taking this approach opens up a number of interesting possibilities. For instance, the user can choose to dispense with the hardware roundkey expansion completely, in situations where it is preferable to generate the expanded roundkeys off-line in software, to save both logic resource and power. Or alternatively, roundkey expansion hardware can be shared between multiple encryption/decryption cores, again to lower the required logic real-estate requirements, where this approach is appropriate. These options are unique to Helion; if you would like to learn more about this, or need some background on the AES algorithm and roundkeys, please request our "Full" AES datasheet.

Since AES is being used in so many varied end products, we offer a range of four AES core families, each with different gatecount/speed combinations, so that you can choose the most efficient for your application. We are proud to say that our solutions are class leading in each category.

#### size

The Helion

TINY AES cores

are designed for

ultra-low resource

requirements, and

throughputs up to the

30Mbps range. These

are the very smallest

solutions available for

AES in ASIC.

The Helion **STANDARD** AES cores offer the ultimate in gate efficiency, and throughputs up to the 500Mbps range.

These are the smallest medium data rate solutions available for AES in ASIC.

The Helion **FAST** AES cores go all out for speed, and are usable for data rates in excess of 3Gbps. These are some of the most gate efficient low latency solutions available for AES in ASIC.

The Helion **GIGA**AES cores are

designed for ultra

high data rates, in

excess of 40Gbps.

These are the very

fastest solutions

available for AES in

ASIC.

max data rate

#### Core Choice

The choice of core family is very application specific, driven mainly by the data throughput required, and also by the space available in the target technology.

The Helion **TINY** AES core is an ideal solution when your data throughput requirements fall below 30Mbps, and your application is highly sensitive to resource utilisation; perfect for high volume consumer applications.

For higher data rates, the Helion **STANDARD** AES core suits a large number of modern applications, where it offers higher throughput capabilities in the hundreds of Mbps region, coupled with the advantage of its incredibly small size.

However, if your application data rate is measured in low Gbps, the Helion **FAST** AES cores offer a combination of low latency and high throughput; ideal for situations which make use of feedback modes at higher data rates.

And if this still is not enough throughput for your application, the Helion **GIGA** AES cores should fit the bill, with encryption capabilities well in excess of 40Gbps available.

The following pages cover our most popular solutions, the STANDARD and FAST cores, in some more detail. If you are more interested in the Helion TINY or GIGA AES cores, please contact Helion for specific literature.

## The Helion STANDARD AES cores

The Helion STANDARD AES cores have been carefully designed to require the absolute minimum of logic resource, whilst still maintaining high data throughput capabilities, squarely within the most widely used range, up to 500Mbps.

The implementation approach taken was to split the 128-bit AES data block into four 32-bit words; each AES round then takes four master clock cycles to process, and all the interfaces (plaintext, ciphertext and key) are 32-bits wide.

The interface provided is very straightforward, and will integrate into any existing system with ease. The core interface signal timing has been designed so that the plaintext, ciphertext and AES key ports will talk seamlessly with registers, RAMs or FIFOs. Once started, the Helion core handles all of the data and key word access timing without any further user intervention.

Example performance and logic utilisation figures are shown below, targeting a generic 0.13um CMOS library. Different end technology may obviously have a large impact on these figures. For fine-grain FPGA applications, performance and gate count will be very much dependant on the specific technology targeted; hence figures are not quoted here, but we would be more than happy to supply specific details on request.

If you would like additional information on the Helion STANDARD AES cores, we have a much more detailed datasheet available. This includes specific core interfacing information, additional performance and utilisation figures including decryption, and a fixed 128-bit keysize version, plus some essential background information. If this sounds of interest, we are more than happy to email this out on request.

## The Helion FAST AES cores

The Helion FAST AES cores have been carefully designed to achieve the ultimate in data throughput, along with minimum latency. This makes them ideal for applications requiring data rates up to 3Gbps, and where feedback is necessary, for example in many of the common Block Cipher modes.

The implementation approach taken was to handle the 128-bit AES data block in one go; each AES round then takes just one master clock cycle to process, and all the interfaces (plaintext, ciphertext and key) are 128-bits wide, which is ideal where high performance is required.

The interface to the core has been designed to be extremely simple to use, and will integrate seamlessly into any kind of system. The plaintext, ciphertext, and AES keys may be stored in registers, RAMs, or FIFOs, and the core can be used with the absolute minimum of effort and additional logic.

Example performance and logic utilisation figures are shown below, targeting a generic 0.13um CMOS library. Different end technology may obviously have a large impact on these figures. For fine-grain FPGA applications, performance and gate count will be very much dependant on the specific technology targeted; hence figures are not quoted here, but we would be more than happy to supply specific details on request.

If you would like additional details on the Helion FAST AES cores, we have a much more detailed datasheet available. This includes specific core interfacing information, additional performance and utilisation figures including those for the option to expand roundkeys off-line, plus some essential background information. If this sounds of interest, we are more than happy to email this out on request.

## Standard and Fast AES core performance and resource requirements

|                                           | ——— Standard                               | encryptor ——                               | ——— Fast encryptor ———                       |                                              | — Fast encryptor and decryptor —             |                                              |  |

|-------------------------------------------|--------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|--|

| options                                   | off-line roundkey expansion (all keysizes) | hardware roundkey expansion (all keysizes) | hardware roundkey<br>expansion (128-bit key) | hardware roundkey<br>expansion (256-bit key) | hardware roundkey<br>expansion (128-bit key) | hardware roundkey<br>expansion (256-bit key) |  |

| technology                                | 0.13um CMOS                                | 0.13um CMOS                                | 0.13um CMOS                                  | 0.13um CMOS                                  | 0.13um CMOS                                  | 0.13um CMOS                                  |  |

| typical core logic resource               | <6k gates<br>(plus roundkey RAM)           | <11k gates<br>(no RAM required)            | <27k gates<br>(no RAM required)              | <31k gates<br>(no RAM required)              | <57k gates<br>(plus roundkey RAM for dec)    | <60k gates<br>(plus roundkey RAM for dec)    |  |

| typical master clock                      | >250MHz                                    | >250MHz                                    | >250MHz                                      | >250MHz                                      | >250MHz                                      | >250MHz                                      |  |

| typical data rate<br>(at defined keysize) | >500Mbps                                   | >500Mbps                                   | >3Gbps                                       | >3Gbps                                       | >3Gbps                                       | >2Gbps                                       |  |

For our figures above, we have targeted our most popular core combinations at a generic 0.13um CMOS library. Please feel free to contact us for figures specific to your target application.

## Ordering Information

Before ordering it is necessary to decide which of our range of AES cores will best fit your application. Decide between the TINY, STANDARD, FAST and GIGA families, according to data throughput required and logic resource available. Then, determine whether you require encryption cores, decryption cores, or both; this will be determined by your application, as well as the block cipher mode you are planning to use. And finally, decide if you require the Roundkey expansion to be handled by the hardware, and if so, which AES keysizes you would like to use.

If some of these choices are unclear, or you would just like to go over the options, we are always happy to discuss the alternatives and suggest the most viable solutions. More information is also available in our family specific AES datasheets, which are available on request.

| Base core family | encrypt<br>only | decrypt<br>only | encrypt & decrypt | hardware<br>roundkey expansion | offline<br>roundkey expansion | 128-bit<br>keys | 192-bit<br>keys | 256-bit<br>keys |

|------------------|-----------------|-----------------|-------------------|--------------------------------|-------------------------------|-----------------|-----------------|-----------------|

| TINY             | ✓               | ✓               | ✓                 | ✓                              | ✓                             | ✓               | $\checkmark$    | ✓               |

| STANDARD         | ✓               | ✓               | $\checkmark$      | ✓                              | ✓                             | ✓               | $\checkmark$    | $\checkmark$    |

| FAST             | $\checkmark$    | $\checkmark$    | $\checkmark$      | ✓                              | ✓                             | $\checkmark$    | $\checkmark$    | $\checkmark$    |

| GIGA             | ✓               | ✓               | $\checkmark$      | ✓                              | ✓                             | ✓               | $\checkmark$    | ✓               |

## **About Helion**

Helion is a small well established British company based in Cambridge, England, offering a range of product-proven Data Security silicon IP cores backed up by our highly experienced and professional design service capabilities.

Although we specialise in providing the highest performance data encryption and authentication IP, our interest does not stop there. Unlike broadline IP vendors who try to supply a very diverse range of solutions, being specialists we can offer much more than just the IP core.

For instance, we are pleased to be able to supply up-front expert advice on any security applications which might take advantage of our technology. Many of our customers are adding data security into their existing systems for the first time, and are looking for a little assistance with how best to achieve this. We are pleased to help with suitable advice and support where necessary, and pride ourselves in our highly personal approach.

In addition, our Design Services team have an impressive track record in the development of real security products for our customers; we are proud to have been involved in the design of numerous highly acclaimed security products. This knowledge and experience is fed back into our IP cores, to ensure that they are easy to integrate into real systems, and perform appropriately for real engineering applications.

Unlike many broadline IP core vendors, Helion also spends a great deal of effort designing its cores at the very lowest level. We strongly believe that if you are buying IP, it should have been designed with the ultimate in care, and crafted to achieve the desired performance; not just put together at a high level to get the job done quickly. We find that this approach pushes the results much closer to the intended performance envelope.

For instance, if we are aiming for speed, we carefully optimise the datapath delays at gate level; the result is a significantly faster core than if we had taken a more removed view of the problem. Similarly, if we are aiming at reducing the gate count, we maintain a detailed understanding of gate budget throughout the design process. The benefits of this low and detailed approach to design can be clearly demonstrated by direct comparison between Helion AES cores and the equivalents from other vendors.

## More information

For more detailed information on this or any of our other products and services, please contact Helion and we will be pleased to discuss how we can assist with your individual requirements.